FPGAs contain a fix number of resources. These resources are components like BlockRAM, FlipFlops, LUTs, etc. An application design must be mapped into these resource components.

FPGA resources:

-

BlockRAM is an FPGA-integrated memory used for saving FPGA internal data.

-

FlipFlops are electronic circuits used for storing logical state information.

-

LUTs (look-up-tables) are used for implementation of logic functions (AND, OR, XOR, etc.).

-

RAM LUTs are LUTs-related FPGA internal memories.

-

Embedded arithmetic logic units (ALUs or "embedded multipliers"") are hardware multipliers integrated into the FPGA.

How many resources you can use for implementing a design depends on the type of the FPGA.

![[Tip]](../common/images/admon/tip.png) |

Resources of Supported Hardware Platforms |

|---|---|

|

In Device Resources, you find information on all supported hardware platforms. |

Every module of a VisualApplets design (except branch, trash, etc.) uses part of the available resources exclusively. Therefore, it is of utmost importance that you are informed about the current state of all resources in use while you are creating your design.

![[Important]](../common/images/admon/important.png) |

No extra resources |

|---|---|

|

You can only use the resources available. |

Information on resource usage of individual operators you find in the operator reference (see, for example, MULT or DIV in the Operator Reference, Arithmetics library).

The current resource usage of a design is in part calculated exactly and in part estimated by VisualApplets. Calculation and estimation are executed in Design Rule Check 2 (DRC2) (see 'Design Rules Check').

Exact calculation of resource usage during Design Rule Check 2:

-

BlockRAM

-

Arithmetic logic units (hardware multipliers)

Estimation of resource usage during Design Rule Check 2:

-

LUT

-

RAM-LUT

-

FlipFlops

Information on the exact resource usage of LUTs, RAM-LUTs and FlipFlops is only available after a successful build of an applet.

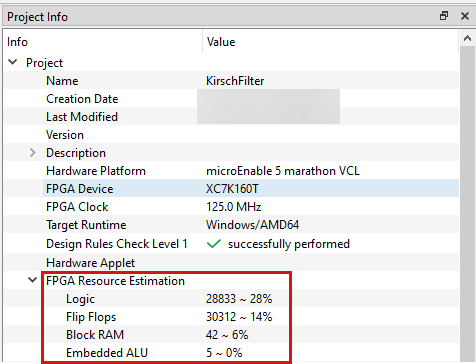

After Design Rule Check 2, the absolute result of the FPGA resource usage (followed by the percentage usage) for the complete design is displayed in the information panel, tab Project Info, section Project/Resources (see 'Project Info').

The resource usage of a design depends on the parallelism (link parameter) used in the design, and on the number and complexity of the modules deployed.

![[Important]](../common/images/admon/important.png) |

Keep Parallelism Low |

|---|---|

|

In order to save resources, you should always try to keep the parallelism of a design as low as possible when defining the settings for the required band width (see description of operator PARALLELdn in Operator Reference). |

![[Important]](../common/images/admon/important.png) |

Estimated Values and Successful Build |

|---|---|

|

If resource estimation values are slightly below 100%, build might fail. On the other hand, even if resource estimation values are slightly over 100%, build might be successful. This is due to the fact that the values are only estimated and the actual resource usage might be slightly higher or lower. |

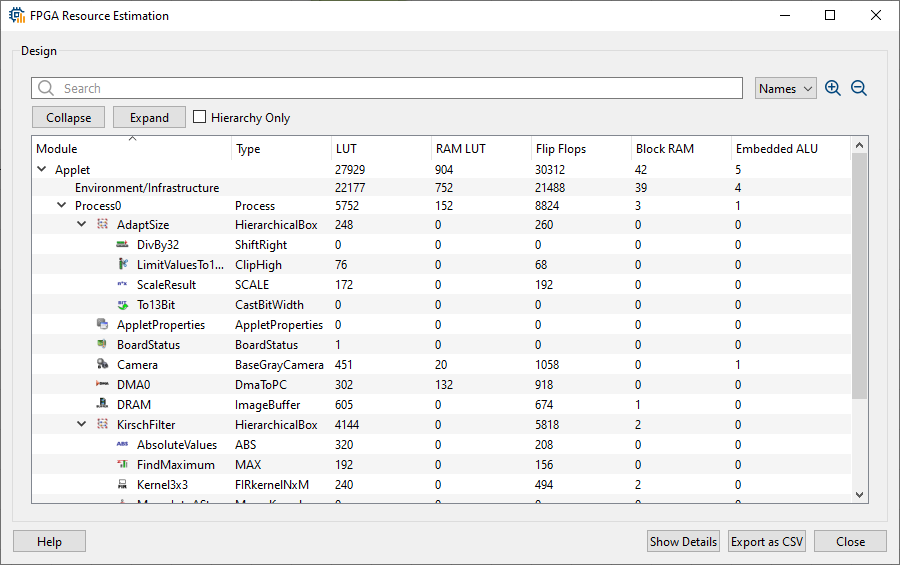

Detailed information on the resource usage of the entire design as well as on the resource usage of each individual

module you can obtain by selecting from the main menu →

or by clicking the button

.

.

For further comparison, you can export the estimated values as a coma-separated values (CSV) file by clicking the button.

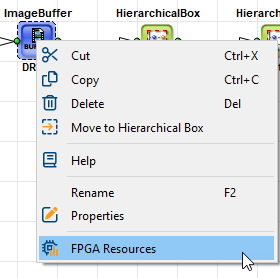

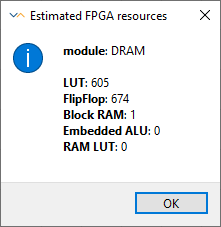

You can access information on the estimated FPGA resource usage of an individual module via the context menu (right-click), selecting .

Prev

Prev