The design rules check (DRC) is an elementary function of VisualApplets. A design rules check checks if a VisualApplets project does not contain any design errors. Projects which do not pass the DRC can not be build or some functions are disabled.

The DRC log window which is part of the dock, lists the progress and results of the DRCs. It shows important information on design errors and resource usage estimations. Some windows include a DRC log as a sub-window. The DRC log can be saved in a HTML file using a right click in the text and the selection of on the pop-up menu.

In VisualApplets includes two levels of design rules checks. DRC level 1 and DRC level 2 which are explained in detail in the following sections.

The DRC level 1 checks the integrity of the project. Click on → ( Ctrl+F7 ) or use the icon Design Rules Check Level 1 from the Build icon bar to start the DRC level 1. Besides the direct access, the DRC level 1 is automatically started by other VisualApplets functions such as simulation, resource estimation, or build process. The DRC level 1 checks amongst others whether

-

no open ports exist in a design.

-

no link is in conflict state.

-

no operator parameter is in conflict state.

-

no conflicts for device resources exist.

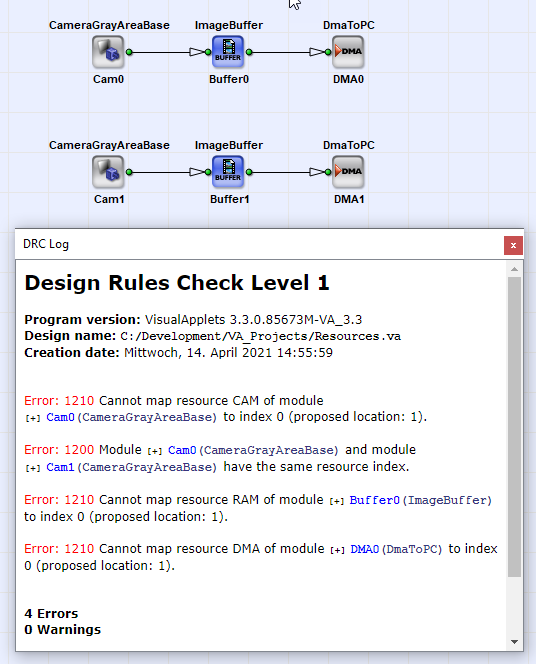

The following figure shows four errors reported by the DRC level 1. In this example, three device resource conflicts of the resources CAM, RAM, and DMA are shown as well as a resource index conflict of Cam0 and Cam1. You can simply click on the module name to highlight the module in the diagram which causes the error. This is very useful in complex projects with many diagram windows.

The DRC level 2 can only be started after a successful DRC level 1. However, starting the DRC level 2 by a click on → ( Ctrl+F8 ) or a click on the icon Design Rules Check Level 2 from the Build icon bar will automatically start DRC level 1, too. Besides the direct access, the DRC level 2 is automatically started by other VisualApplets functions such as the resource estimation and build process. The DRC level 2 performs a low level design rules check and estimates the required FPGA resources.

Prev

Prev